This July, it has been terribly warm here in Borås, Sweden, almost tropical climate.

Now, I have been terribly affected by this climate, so I obviously became insane.

So what happened really, well, I was sitting and having a Guinness and a malt, thinking of what to do.

Then I realized, I must build my self a computer, a proper one.

WTF, you probably Thinks, thats no strange with that, just take a Mobo, a Processor and some Graphics, and off you go.

Well, you could not be more wrong.

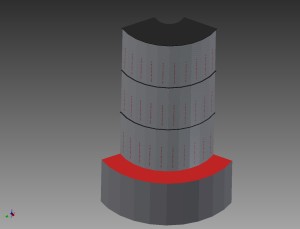

What I am going to build is a proper computer, based on pure ECL technology, like the old CRAY-1 (hense the name of the site), but I am not going to use any intergrated circuits as Samuel Cray did, but discrete bipolar technology, just plain transistors and resistors, nothing else, but loads of them, (hence the name of the site again).

I estimate that I will use about som 5-6000 transistors and the same amount of resistors, if this isn’t proof for insanity, I do not know what is.

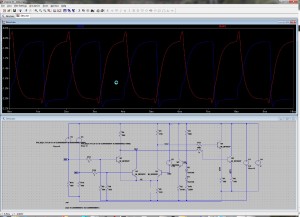

Now I will update with schematics, simulations, thougts etc, when it happens, and at the end photos and other things.

![Mixed-Mode Simulator ( Circuit _ 1-BIT_ALU - Page _ MAINPAGE ) [Project _ ECL] Page _ 1](http://www.microdiscray.com/wp-content/uploads/2014/07/Mixed-Mode-Simulator-Circuit-_-1-BIT_ALU-Page-_-MAINPAGE-Project-_-ECL-Page-_-1-300x212.jpg)

![Schematic Editor ( Circuit _ 1-BIT_ALU - Page _ MAINPAGE ) [Project _ ECL] Page _ 1](http://microdiscray.com/wp-content/uploads/2014/07/Schematic-Editor-Circuit-_-1-BIT_ALU-Page-_-MAINPAGE-Project-_-ECL-Page-_-1-300x212.jpg)

![Schematic Editor ( Circuit _ 1-BIT_ALU - Page _ REG ) [Project _ ECL] Page _ 1](http://microdiscray.com/wp-content/uploads/2014/07/Schematic-Editor-Circuit-_-1-BIT_ALU-Page-_-REG-Project-_-ECL-Page-_-1-300x212.jpg)